Mateo Valero, https://www.bsc.es/mateo-valero is professor of Computer Architecture at Technical University of Catalonia (UPC) and is the Founding Director of the Barcelona Supercomputing Center, where his research focuses on high performance computing architectures.

He has published approximately 700 papers, has served in the organization of more than 300 International Conferences and has given more than 800 invited talks. Prof. Valero has been honored with numerous awards, among them: The Eckert-Mauchly Award 2007 by IEEE (Institute of Electrical and Electronics Engineers) and ACM (Association for Computing Machinery), the Seymour Cray Award 2015 by IEEE and the Charles Babbage 2017 by IEEE. Among other awards, Prof. Valero has received The Harry Goode Award 2009 by IEEE, The Distinguished Service Award by ACM. Prof. Valero is a "Hall of the Fame" member of the ICT European Program (selected as one of the 25 most influential European researchers in IT during the period 1983-2008, Lyon, November 2008). In 2020 he was awarded the "HPCWire Reader's Choice Awards" "for his exceptional leadership in HPC" and for "being an HPC pioneer since 1990 and the driving force behind the renaissance of European HPC independence". He has received two of the 10 national research awards in Spain: the Julio Rey Pastor in Computer Science and Mathematics in 2001, and the Leonardo Torres Quevedo in engineering in 2007. He was awarded the Rey Jaime I prize in basic research in 1997. He received the Aragon Prize in 2008, and the "Creu de Sant Jordi" in 2016, which are the most important awards granted by the Governments of Aragon and Catalonia. City of Barcelona Award in 1994 and Narcís Monturiol Award, awarded by the Generalitat of Catalonia in 1994. Research Award from the "Fundació Catalana per a la Recerca i la Innovació", highest recognition for research in Catalonia, awarded by the Government of the Generalitat, in 2006. Honored with "Condecoración de la Orden Mexicana del Águila Azteca" (2018), highest recognition granted by the Mexican Government for a non-Mexican citizen. Prof. Valero holds Honoris Causa doctorates from the following 10 universities: Chalmers University (Göteborg, Sweden, 2008), University of Belgrade (Serbia, 2008), University of Las Palmas de Gran Canarias (2009), University of Veracruz (Mexico , 2010), University of Zaragoza (2011), Complutense University of Madrid (2013), University of Cantabria (2015), University of Granada (2015), the Cinvestav of Mexico (2017) and the Cristóbal Colón University of Veracruz (Mexico, 2022). He is a member of the following 10 academies: Founding Academic of the Royal Academy of Engineering of Spain (1994), Corresponding Academic of the Royal Academy of Exact, Physical and Natural Sciences of Spain, (2005), Academic of the Royal Academy of Sciences and Arts of Barcelona (2006), Academic of the Academia Europaea "Academy of Europe" (2010), Corresponding Academic of the Academy of Sciences of Mexico (2012), Academic of the Academy of Gastronomy of Murcia (2018), Honorary Academic of the Royal European Academy of Doctors (2018), Corresponding Academic of the Academy of Engineering of Mexico (2018), Honorary Academic of the Royal Academy of Medicine of Zaragoza (2021) and Corresponding Academic of the Academy of Sciences of Cuba (2022) . He is a "Fellow" of the IEEE (The Institute of Electrical and Electronics Engineers), the ACM (The Association for Computing Machinery), and the AAIA (Asia-Pacific Artificial Intelligence Association). In 2023, SCALAC (the Advanced Computing System for Latin America and the Caribbean), awarded him a distinction "In recognition of his Outstanding Collaboration in Advanced Computing Between Latin America and Europe" and institutionalized the "Mateo Valero Prize for the Outstanding Collaboration with Latin America and the Caribbean Partners in HPC", which will be awarded on an annual basis. In 1998, he was chosen as the favorite son of his town, and in 2006, the Alfamén school parents' association decided to name the public school where Professor Valero had studied after him.

Naoki Shinjo

Naoki Shinjo

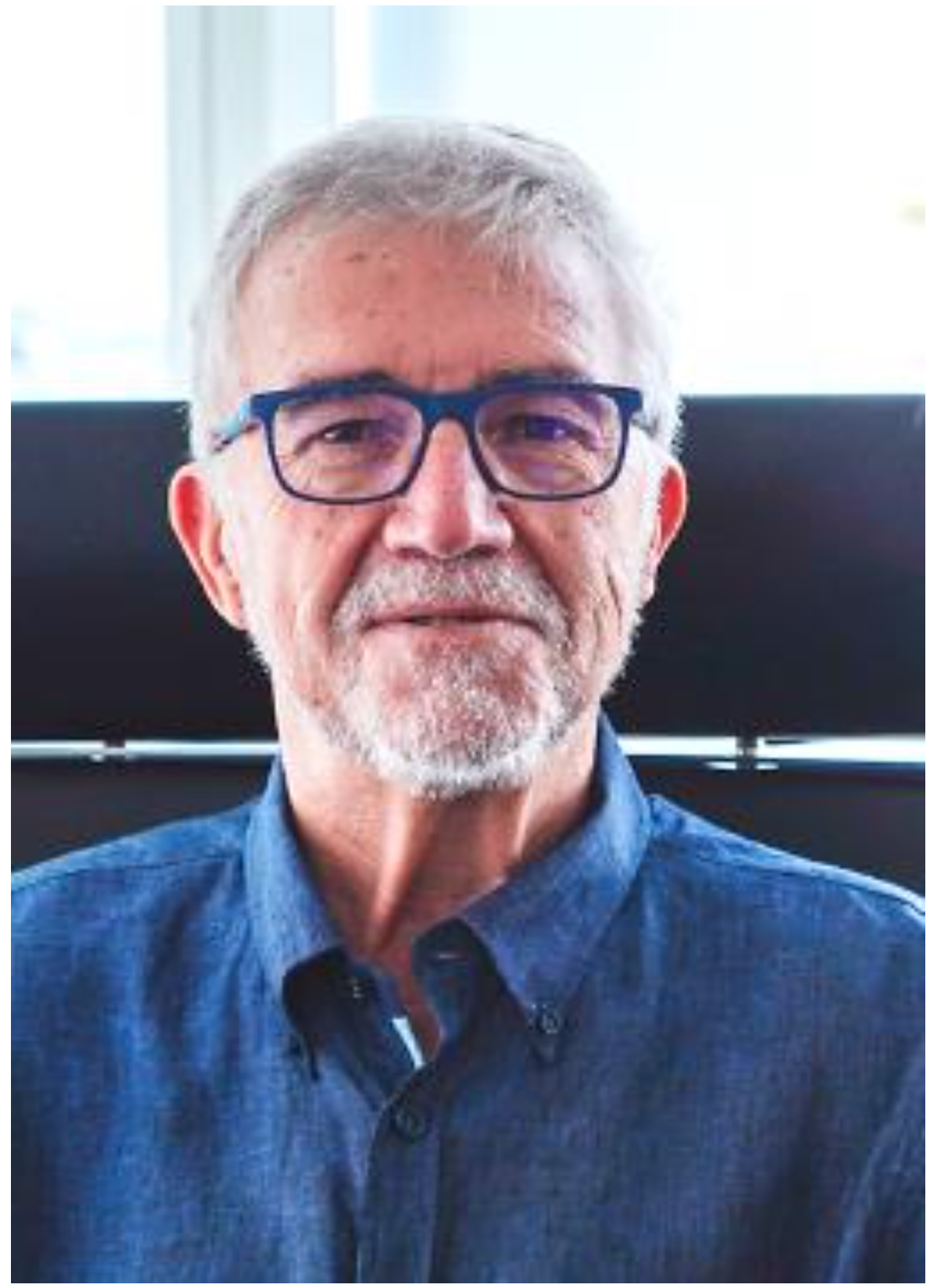

Prof. Mateo Valero

Prof. Mateo Valero

Dr. Michael Gschwind

Dr. Michael Gschwind